- 您现在的位置:买卖IC网 > Sheet目录2000 > IDT82V3255TFG (IDT, Integrated Device Technology Inc)IC PLL WAN SMC STRATUM 3 64-TQFP

IDT82V3255

WAN PLL

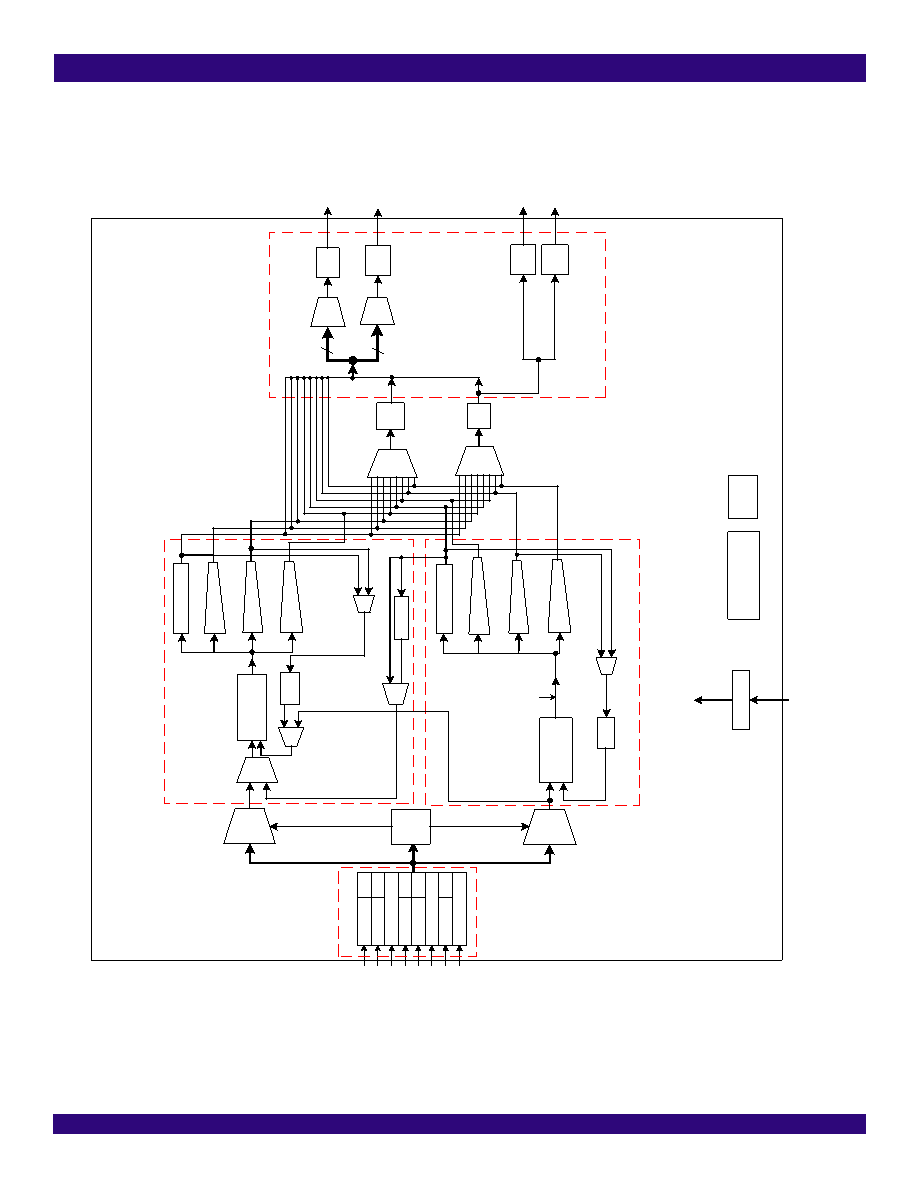

Functional Block Diagram

11

December 3, 2008

FUNCTIONAL BLOCK DIAGRAM

Figure 1. Functional Block Diagram

EX_

SY

NC

3

Mo

ni

to

rs

T0

PF

D

&LP

F

Di

vid

er

T4

P

FD

&LP

F

Div

ide

r

AP

LL

Mic

rop

ro

ce

ss

or

In

te

rfa

ce

JT

AG

PB

O

Ph

as

eO

ffs

et

77

.7

6M

H

z

T4

AP

LL

T0

AP

LL

Di

vi

de

r

OU

T1

OU

T3

MUX

OU

T2

OU

T7

MUX

T4

APL

L

MUX

T0

APL

L

MUX

T4

In

pu

t

Sel

ect

or

T0

In

pu

t

Se

le

ct

or

OS

C

I

77

.7

6M

H

z

16

E1

/1

6T

1

12

E1

/2

4T

1/

E3

/T

3

16

E1

/1

6T

1

12

E1

/2

4T

1/

E3

/T

3

Aut

o

Di

vi

de

r

Aut

o

Di

vid

er

10

T0

DPLL

T4

D

PLL

Input

IN1

_CM

OS

IN

1_

D

IF

F

EX

_S

YNC

1

IN2

_C

M

OS

IN2_

DIFF

EX

_S

YNC

2

IN

3_C

MO

S

FR

SYN

C_

8K

MF

R

SYN

C_

2K

O

utput

G

SM

/G

PS

/16E

1/16T

1

T0

77.7

6

M

H

z

T0

8

kH

z

G

SM/O

BS

AI/

16E1/

16T

1

8k

D

ivi

de

r

Input

Pr

e-

Di

vi

der

Pr

io

rity

Input

Pr

e-

Di

vi

der

Pr

io

rity

Input

Pr

e-

Di

vi

der

Pr

io

rity

Input

Pr

e-

Di

vi

der

Pr

io

rity

Input

Pr

e-

Di

vi

der

Pr

io

rity

Di

vi

de

r

EX

_S

YNC1

EX

_S

YNC2

EX

_S

YNC3

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

IDT82V3280APFG

IC PLL WAN SE STRATUM 2 100TQFP

IDT82V3285AEQG

IC PLL WAN SE STRATUM 100TQFP

IDT82V3285EQG

IC PLL WAN SE STRATUM 100TQFP

IDT82V3288BCG

IC PLL WAN 3E STRATUM 2 208CABGA

IDT82V3355EDG

IC PLL WAN SYNC ETHERNET 64TQFP

IDT82V3358EDG

IC PLL WAN SYNC ETHERNET 64TQFP

IDTCSPT857DNLG8

IC PLL CLK DVR SDRAM 40-VFQFPN

IDTCV105EPVG8

IC CLK GEN DESKTOP PC 48-SSOP

相关代理商/技术参数

IDT82V3255TFG8

功能描述:IC PLL WAN SMC STRATUM 3 64-TQFP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT

IDT82V3255TFGBLANK

制造商:IDT 制造商全称:Integrated Device Technology 功能描述:WAN PLL

IDT82V3280

制造商:IDT 制造商全称:Integrated Device Technology 功能描述:WAN PLL

IDT82V3280_08

制造商:IDT 制造商全称:Integrated Device Technology 功能描述:WAN PLL

IDT82V3280APFG

功能描述:IC PLL WAN SE STRATUM 2 100TQFP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT

IDT82V3280APFG8

制造商:Integrated Device Technology Inc 功能描述:IC PLL WAN SE STRATUM 2 100TQFP

IDT82V3280DQ

制造商:IDT 制造商全称:Integrated Device Technology 功能描述:WAN PLL

IDT82V3280DQG

功能描述:IC PLL WAN SE STRATUM 2 100-TQFP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT